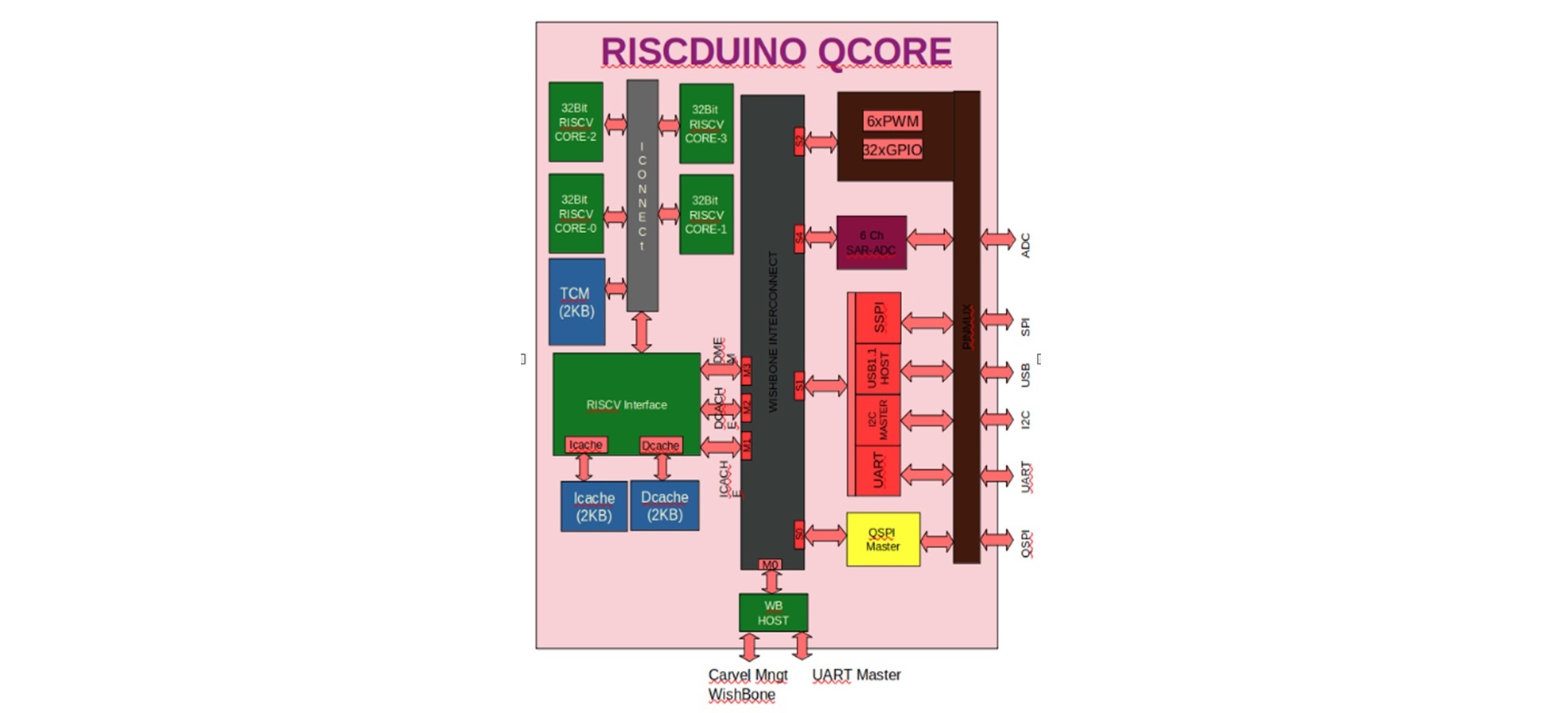

Riscduino is a Quad 32 bit RISC V based SOC design pin compatible to arduino platform.

- Quad 32 Bit RISC-V core

- xxKB SRAM for instruction cache

- xxKB SRAM for data cache.

- xxKB SRAM for Tightly coupled memory - For Data Memory.

- Quad SPI Master with 4 Chip select, supports both SPI flash and SRAM interface.

- 2 x UART with 16Byte FIFO.

- 1 x USB 1.1 Host.

- 1 x USB 1.1 Device.

- 1 x I2C Master & Slave.

- 1 x UART Master.

- Simple SPI Master with 4 Chip select.

- 6 x PWM.

- 3 x Timer (16 Bit), 1us/1ms/1second resolution.

- 2 x ws281x driver.

- 16 Hardware Semaphore.

- FPU (SP) Core.

- AES 128 Bit Core.

- RTC Core.

- Pin Compatbible to arduino uno.

- SoC integration support.

- Verification suite provided..

- Xlinux FPGA development platform.

- Tool flow support for Zephyr OS.

- Tool flow support for MicroPython.

- Support for efabless MPW tapout in Sky130nm.

- Design works both commerial and openlane flow.